# Systems Approach To Effective Diagnostics & Prognostics

**DSI International**

07/23/2003

# Our Company

# **28 YEARS of TECHNICAL SERVICE**

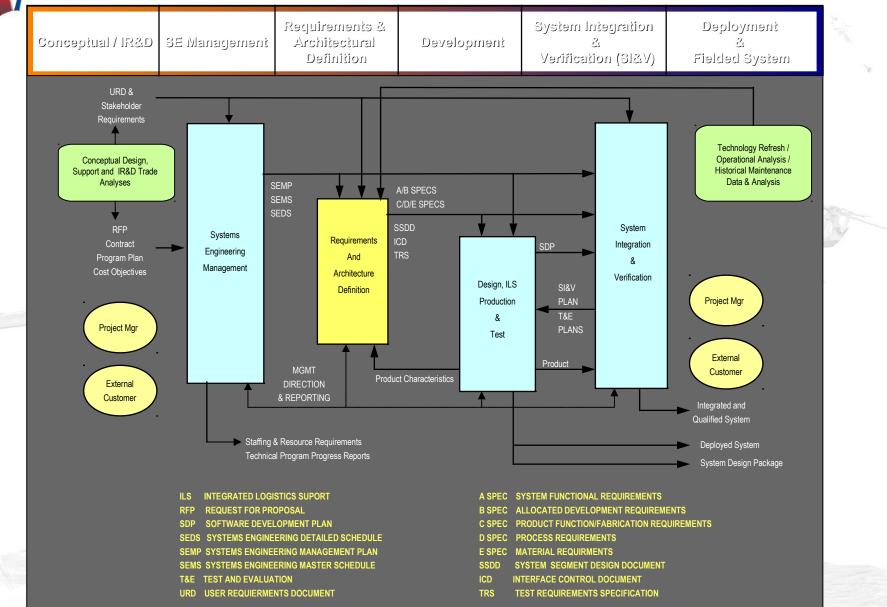

### A Systems Engineering Approach to <u>Integrated</u> Diagnostics and Prognostics

Requirements Derivation

Requirements Flow down

Design Development

Design Optimization

Embedded Systems

Life Cycle Support

### express

# **Performance Risk Defined**

#### Performance Risk is

- *Uncertainty* in the ability of a design to meet the specified performance level *and* the *consequences* thereof

- The gap between the validated and specified performance levels and the consequences of that gap

- "Performance" is defined broadly to include

- Operability, Functionality, **Safety**, Testability, Affordability, Reliability, Availability, Maintainability, *etc*.

- Any dimension of value to the customer

### Today's Technology Provides Process Improvement To *Fill the Gap*

- Enhanced Diagnostics Modeling Provides:

- Improved Fault Detection Confidence (FD%)

- Improved Fault Isolation to Optimum Repair Level (FI%)

- Reduced False Alarms / False Removals (FA%)

- Lower Mean Time to Isolate (MTTI)

- Improved Operational Availability (Ao)

- Improved Safety Through Critical Fault Analysis (FMECA)

- Reduced Life Cycle Cost

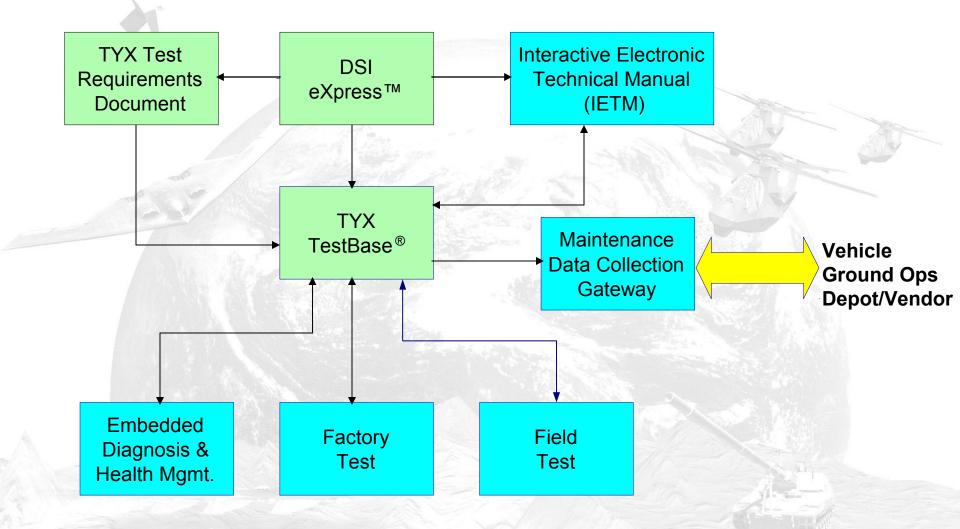

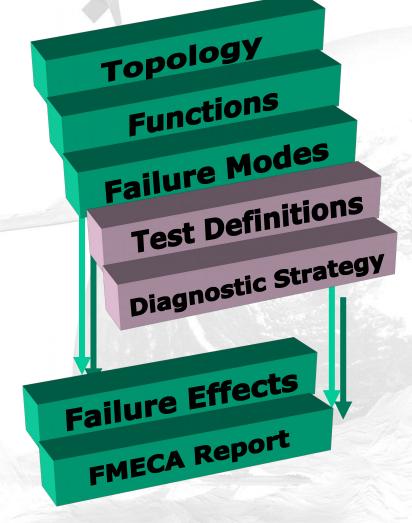

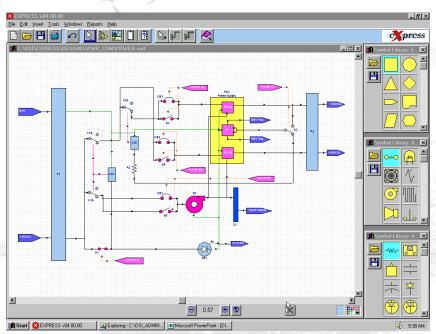

**Development Information Model**

ress

- Topology (Visualization)

- Functions (Objects + Nets)

- Failure Modes (FMECA)

- Test Definitions (Testing)

- Diagnostic Strategy

- Failure Effects (FMECA)

- **FMECA Report**

- Working on DMECA (<u>Degraded</u> Mode Effect and Criticality Analysis)

# **Global Modeling**

- Electrical

- Electronic

- Mechanical

- Hydraulic

- Optical

- Software

- Fully Hierarchical

- Object-Oriented

press

• Networked

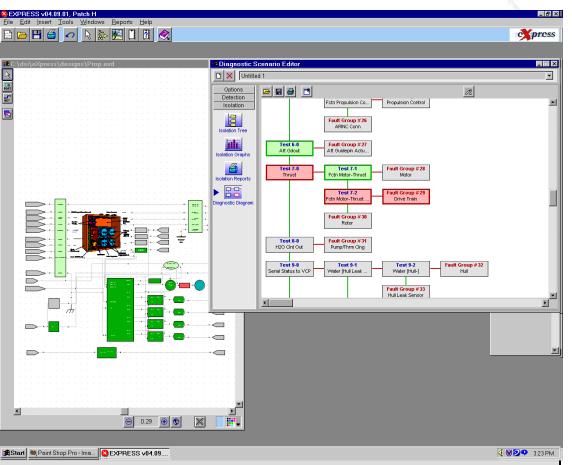

# **Diagnostic Outputs**

#### Diagnostic Fault Tree

ress

Provides an interactive interface to "exercise" the diagnostics.

Provides means to "check" models for validity.

Quickly Identifies problem areas (i.e., Large fault / ambiguity groups)

Can be used for Intelligent troubleshooting

| Light | Green  | - partially | proven | good | - not | yet s | suspecte | d |

|-------|--------|-------------|--------|------|-------|-------|----------|---|

| Croo  | n nrov | on good     |        |      |       |       |          |   |

- Green- proven good

- Light Blue Stimuli necessary for test

- Yellow suspected, in current suspect set

- Teal secondary suspects, not in the current suspects set but could be responsible for a previously performed test that failed

- Dark Red contains potentially failed components, in AG

- Light Red higher level part for which a lower level part is color dark red

- Dark Blue -I/O Test Point

# **FMECA Output**

press

e

| <b>€</b>   % <b>1</b> 6 <b>16</b>   <b>€</b>   •€ | <u>n</u> E | p- p-p-                         | 🔍 🔍 💛 125% 💽                                                           | BIU≣≣≣                                      | ✓ 10                                                                              |                            |          |                         |                |          | 1.0   |         | -    |

|---------------------------------------------------|------------|---------------------------------|------------------------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------|----------------------------|----------|-------------------------|----------------|----------|-------|---------|------|

| Design                                            |            | ltern                           | Failure                                                                | Failure Effect Causes                       | Effects (Local + Next H                                                           | -                          |          | Compensating Provisions | Severity       | Fur      | 1     | elec    |      |

| T. FMECA Study                                    | 1          | X1:A:c_c                        | X1:A:No volatge on output c                                            | X1:A:C_C short c.c.                         | Local<br>X1:A:BIT Failure St 0 at 0ut1<br>X1:A:New Effect                         | Next Higher<br>X1:BIT St 0 |          |                         | l Catastrophic | 2.2      | mech  | project |      |

| Generate                                          | 2          |                                 | X1:A:Ripple on output C                                                | X1:A:C_C open c.c.                          | X1:A:BIT Failure St 1 at Out1<br>X1:A:New Effect                                  | X1:BIT St 1                | Bit One  |                         | III Marginal   | 2.2      |       |         |      |

|                                                   |            | X1:A:d1                         |                                                                        | X1:A:Output Port d1 from b1,c1 short c.c.   | X1:A:New Effect                                                                   |                            |          |                         | I Catastrophic |          | ŝymio | anno    |      |

|                                                   | <u> </u>   |                                 | X1:A:Failure transmission 1 on c1                                      |                                             | X1:A:BIT Failure St 0 at 0ut2<br>X1:A:New Effect                                  |                            |          |                         | l Catastrophic |          |       |         |      |

|                                                   | 5          | X1:A:opt_e1                     | X1:A:Failure transmission 1 on e1                                      |                                             | X1:A:BIT Failure St 0 at 0ut2<br>X1:A:New Effect                                  |                            |          |                         | I Catastrophic |          |       |         |      |

|                                                   | 6          | 364 · 0 ·                       | X1:A:Failure transmission 1 on e1<br>X1:A:Failure transmission 1 on b1 |                                             | X1:A:BIT Failure St 0 at 0ut2<br>X1:A:New Effect                                  |                            |          |                         | I Catastrophic |          |       |         |      |

|                                                   |            | X1:A:r a                        | X1:A:Tailure transmission For br<br>X1:A:Too high volatge on output A  | -                                           | X1:A:BIT Failure St 0 at 0ut2<br>X1:A:New Effect<br>X1:A:BIT Failure St 1 at 0ut1 |                            |          |                         | I Catastrophic | 2.2      |       |         | ally |

|                                                   | 0          | A191_8                          | X1:A:No voltage on output A                                            | X1:A:R_A open c.c.                          | X1:A:New Effect<br>X1:A:BIT Failure St 0 at 0ut1                                  |                            |          |                         | I Catastrophic |          |       |         |      |

|                                                   | 10         | X1:A:r_a1                       | X1:A:Failure transmission 1 on a1                                      |                                             | X1:A:BIT Failure St 0 at 0ut2                                                     |                            |          |                         | I Catastrophic |          |       |         |      |

|                                                   |            |                                 | X1:A:Failure transmission 1 on d                                       | _                                           | X1:A:New Effect<br>X1:A:BIT Failure St 0 at 0ut1                                  |                            |          |                         | I Catastrophic |          |       |         |      |

|                                                   | 12         |                                 | X1:A:Failure transmission 0 on d                                       | X1:A:input port Vm_D open c.c.              | X1:A:BIT Failure St 1 at Out1                                                     | X1:BIT St 1                | Bit One  |                         | III Marginal   | 2.2      |       |         |      |

|                                                   | 13         | X1:A:vr_b                       | X1:A:No volatge on output b                                            | X1:A:Vr_B open c.c.                         | X1:A:New Effect<br>X1:A:BIT Failure St 0 at 0ut1                                  | X1:BIT St 0                | Bit Zero |                         | I Catastrophic | 2.2      |       |         |      |

|                                                   | 14         |                                 | X1:A:Too high volatge on output b                                      | X1:A:Vr_B short c.c.                        | X1:A:BIT Failure St 1 at Out1<br>X1:A:New Effect                                  | X1:BIT St 1                | Bit One  |                         | III Marginal   | 2.2      |       |         |      |

|                                                   | 15         | X1:B:c_c                        | X1:B:No volatge on output c                                            | X1:B:C_C short c.c.                         | X1:B:BIT Failure St 0 at Out1<br>X1:B:New Effect                                  | X1:BIT St 0                | Bit Zero |                         | I Catastrophic | 2.2      |       |         |      |

|                                                   | 16         |                                 | X1:B:Ripple on output C                                                | X1:B:C_C open c.c.                          | X1:B:BIT Failure St 1 at Out1<br>X1:B:New Effect                                  | X1:BIT St 1                | Bit One  |                         | III Marginal   | 2.2      |       |         |      |

|                                                   |            | X1:B:d1                         |                                                                        | X1:B:Output Port d1 from b1,c1 short c.c.   | X1:B:BIT Failure St 0 at 0ut2<br>X1:B:New Effect                                  | X1:BIT St 0                | Bit Zero |                         | I Catastrophic | 4.5      |       |         |      |

|                                                   |            |                                 | X1:B:Failure transmission 1 on c1                                      |                                             | X1:B:BIT Failure St 0 at 0ut2<br>X1:B:New Effect                                  |                            |          |                         | I Catastrophic |          |       |         |      |

|                                                   |            |                                 | X1:B:Failure transmission 1 on e1                                      |                                             | X1:B:BIT Failure St 0 at 0ut2<br>X1:B:New Effect                                  |                            |          |                         | I Catastrophic |          |       |         |      |

|                                                   | 20         |                                 | X1:B:Failure transmission 1 on e1<br>X1:B:Failure transmission 1 on b1 |                                             | X1:B:BIT Failure St 0 at 0ut2<br>X1:B:New Effect<br>X1:B:BIT Failure St 0 at 0ut2 |                            |          |                         | I Catastrophic |          |       |         |      |

|                                                   | 12/20      | X1:B:rv_p1                      | X1:b:Failure transmission 1 on b1<br>X1:b:No voltage on output A       | X1:B:RV_B1 short c.c.<br>X1:B:R_A open c.c. | X1:B:New Effect<br>X1:B:New Effect<br>X1:B:BIT Failure St 0 at 0ut1               |                            |          |                         | I Catastrophic |          |       |         |      |

|                                                   | 1          | Autor_a                         | Transition foldage on output M                                         | Arreat_r operios                            | And Shiring Store Out                                                             | Anon ot 0                  | 511 2010 |                         | - carastrophic | <u>}</u> |       |         |      |

|                                                   | 100000     | Detail Hierarchy   FMECA Errors |                                                                        |                                             |                                                                                   |                            |          |                         |                |          |       |         |      |

|                                                   | Title      | e                               | xxx                                                                    |                                             |                                                                                   |                            |          |                         |                |          |       |         |      |

|                                                   | Pur        | pose                            |                                                                        |                                             |                                                                                   |                            |          |                         |                |          |       |         |      |

|                                                   |            |                                 |                                                                        |                                             |                                                                                   |                            |          |                         |                |          |       |         |      |

|                                                   |            |                                 |                                                                        |                                             |                                                                                   |                            |          |                         |                |          |       |         |      |

|                                                   |            |                                 |                                                                        |                                             |                                                                                   |                            |          |                         |                |          |       |         |      |

|                                                   |            |                                 |                                                                        |                                             |                                                                                   |                            |          |                         |                |          |       |         |      |

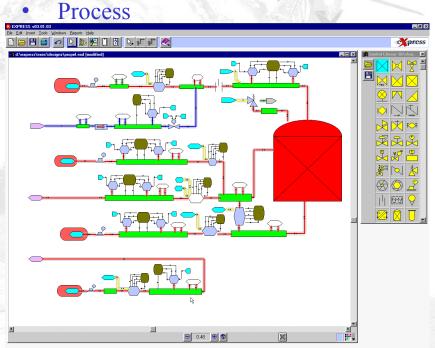

# **Process Interoperability**

Press Typical Model Types Developed or Supported

•Reliability

•Provides Data to Diagnostics Models

FunctionalDependencyFailure Mode

Design Direction Design Assessment Design Optimization Support to Ground Operations

Rule Base

Case Base

Model Based Reasoner (MBR)

AI

Prognostic

Higher Order Run Time

**Require Developed System**

Derive Information from Functional, Dependency and Failure Information

Support to Optimization Studies DSI International

### **Systems Process at Work**

- RAH-66 Comanche Program

- Boeing-Sikorsky-US Army

#### Diagnostic Design Requirements Analysis Guide (DDRAG)

Note: Document contents are export restricted with distribution limited to US Government agencies

For Distribution and questions, please contact:

Steve Desantis Boeing 610-591-6558 stephen.f.desantis@boeing.com

### **Systems Process at Work**

#### DDRAG Purpose

- Comanche Team Desktop Reference

- Ensures Standard Processes and Procedures for All Levels of Diagnostics Design Development

- Identifies Processes Needed to Define Diagnostics Design Requirements

- Equipment

- Subsystems

- System / Segment

- Air Vehicle

- External Diagnostics

- Defines Operational Flight Program and Off-Board Diagnostics Requirements

### Design Process management

- All Levels of Design Data and Tools Need to be Interoperable

- Tools Need to Support Open Information Architecture

- Process Needs to be Managed Through an Integrated Product Development Environment (IPDE)

- A Concept Development System was Developed for NASA on the 2<sup>nd</sup> Gen RLV / SLI Project to Meet the Interoperability Needs

- IVHM Systems Management Environment (ISME)

- Data Management

- Translation between Tools, Data and ISME

- Version / Configuration Control

- Audit Trail Management

- User Control

- Security

ress

### Important Enterprise Features